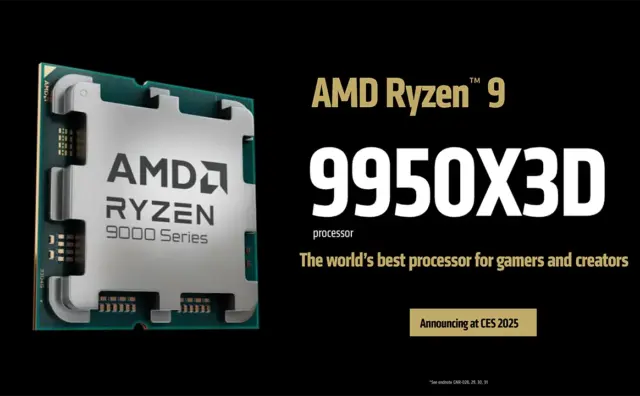

先日、Ryzen 9000X3Dシリーズの上位CPU「Ryzen 9 9950X3D」および「Ryzen 9 9900X3D」が発表されました。

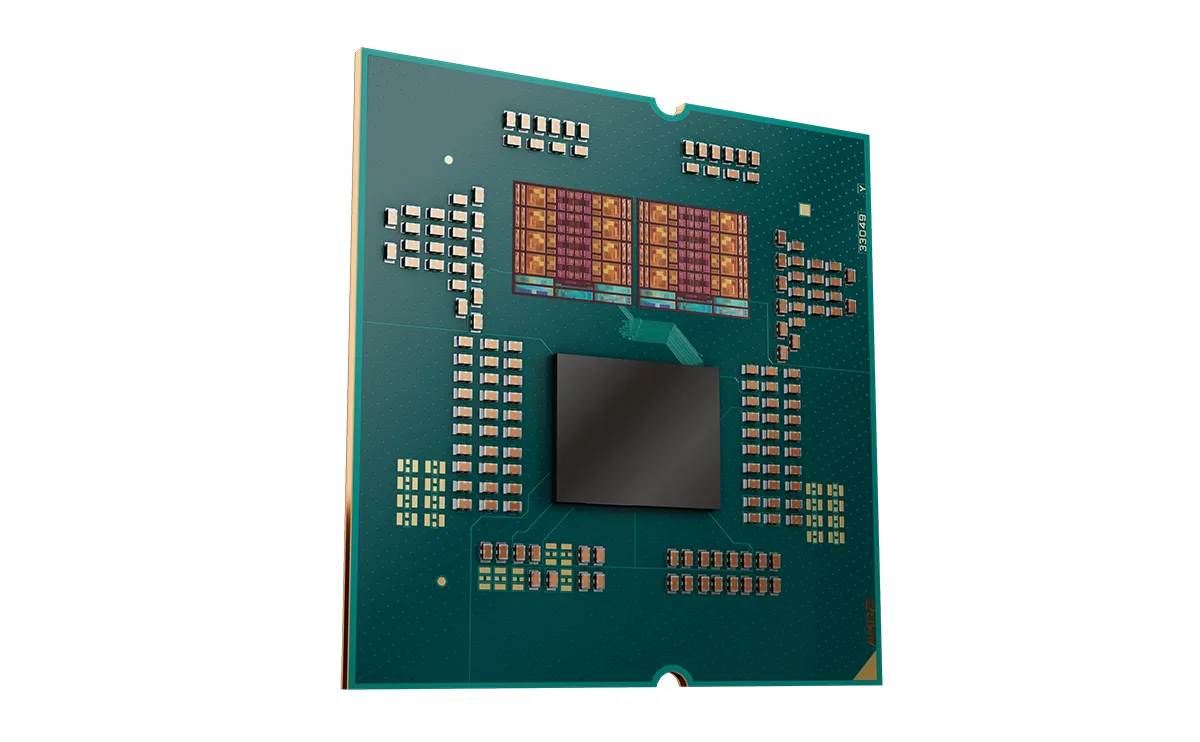

前世代と同様に3D V-Cace CCD+通常CCD構成で、一部で期待されていた“デュアル3D V-Cache CCD”構成とはならず、ガッカリという人もチラホラ見かけたりします。

両CCDに3D V-Cache搭載のRyzen X3Dが投入されてこなかった理由について、今まで公式に説明されたことはありませんでしたが、CES 2025にてHardwareluxxがAMDから回答を得られたようです。

AMD「技術的な障壁はない」「作ろうと思えば作れる」

我々がAMDに、両方のCCDに3D V-Cacheを搭載したRyzenがまだ登場していない技術的理由があるのか質問したところ、驚くべきことに「技術的な理由や課題は存在しない」という回答が得られた。

AMDによると、両CCDに3D V-Cacheを搭載したRyzen X3Dプロセッサが技術的に作れないという訳ではないとのこと。

実際AMDは、Ryzen 9000X3Dシリーズと同じく第2世代3D V-Cacheテクノロジーを採用した、Zen4ベースのサーバー向けCPU「EPYC 9004X」シリーズにおいて(CCXがZen4とZen5という違いはあれど)3D V-Cache搭載CCDを複数搭載したCPUを製品化しているので、「それはそうだろう」という話ではある。

高コストの割にゲーム性能の改善には繋がらないので“低コスパ”

では、なぜ9000X3Dで両CCDに3D V-Cacheを搭載しなかったのでしょうか?

デュアル3D V-Cache CCD設計のプロセッサが発売されていない理由は、単純にコストが高すぎることと、ゲーム用途においては、2つ目のCCDに3D V-Cacheを搭載しても、(Ryzen 7 5800X3Dで)L3キャッシュを32 MBから96 MBへ強化したときのような(劇的な)性能向上には繋がらないという。

最大の理由は“製造コストが高すぎるため”。当然ながらSRAMが増える分のコストが増え、TSV(シリコン貫通電極)などの高度な積層技術のコスト、作業工程と構成する半導体の増加による歩留まりの低下と、様々なコストが製品価格に上乗せされることになります。

またゲーム用途においては、2つ目のCCDに3D V-Cacheを搭載することで得られる利点が小さいというのも理由として挙げられています。

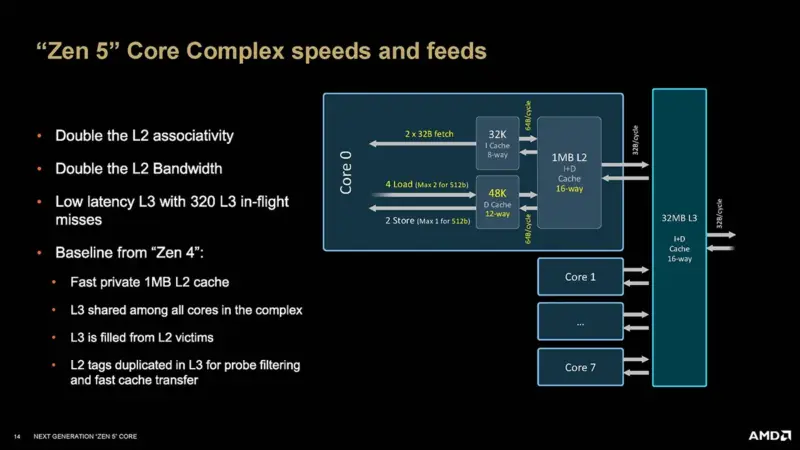

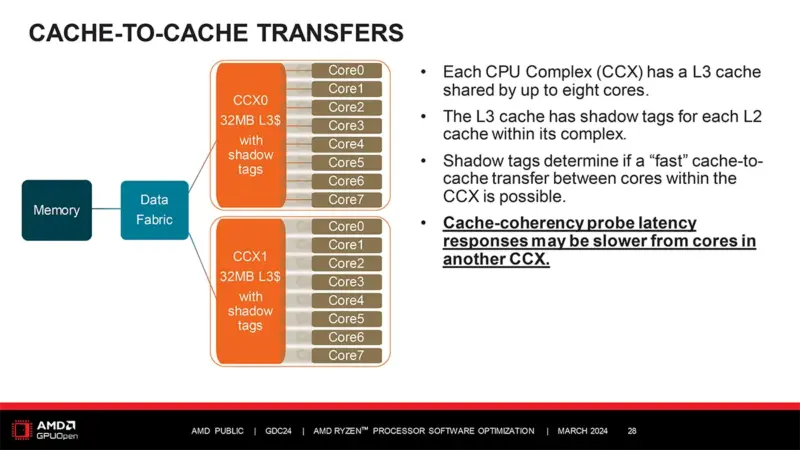

RyzenのCCD同士は独立しており、IOダイ(のData Fabric)を介して接続されている存在です。

発売時にも言及しましたが、「CCDを跨いだキャッシュ処理=Data Fabric経由の通信が発生する」という構造なので、ゲームのような複雑かつインタラクティブでリアルタイム処理が要求される用途では、このData Fabricの速度がボトルネックとなり、折角の巨大なキャッシュの効果も完全には発揮できないというわけです。

Zen6でのCCDあたりコア数増/IOD高速化に期待

もちろんEPYCで3D V-Cache CCDをドカ盛りしたCPUを製品化している以上、CCDを跨ごうが大量のL3キャッシュが効果的に働くワークロードは存在します。しかしゲーム用途においては効果が薄く、コスパが悪いのは確か。

結局はIODの速度が鬼門なので、Zen6以降のアップグレードとしてウワサされている、CCDあたりのコア数増加、IODとの接続帯域の拡大が実現すれば、ゲーム用途のさらなる3D V-Cache増を目指す可能性も高まりそうです。

コメント