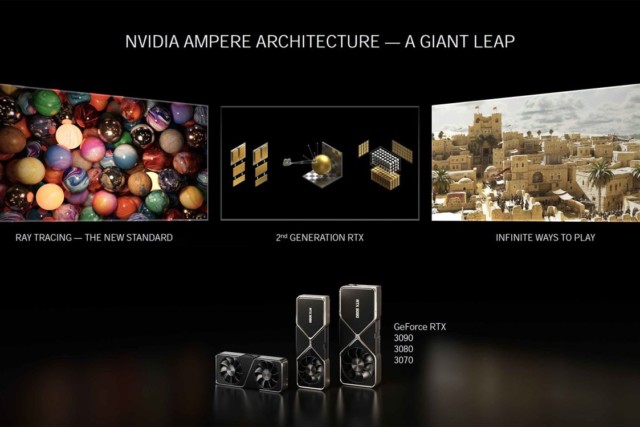

Ampereアーキテクチャに続く、NVIDIAの次世代アーキテクチャについての情報。

以前の噂では、Ampereの後継として投入されるのは“Hopper”アーキテクチャという話でしたが、新たに“Lovelace”アーキテクチャの名前が浮上してきました。

HopperとLovelaceというコードネームは、計算機科学者でありCOBOLの開発者として知られるGrace Murray Hopper、数学者のAda Lovelaceからそれぞれ取られている。

AD102はGA102を超える怪物モノリシックチップに

リーカー (Kopite7kimi)によれば、Lovelaceアーキテクチャの最大コア(AD102と仮称)では、GPC (Graphics Processing Clusters)が最大で12基の構成になるとのこと。Turing世代のTU102ではGPCが6基だったので、2倍に相当する。

リーク情報ではAD102のGPCあたりのTPC (Texture Processor Clusters)は6基で、AmpereのGA102と同数。つまりAD102ではTPCが72 (12*6)、SM (Streaming Multiprocessors)が144 (72*2)となる計算で、CUDAコア数は18,432 (144*128)となる。

単精度浮動小数点数(FP32)演算性能はCUDAコアに比例するため、コアクロック1.8 GHzのGA102が38.7 TFLOPSであることから、AD102は同クロック時に1.71倍の66.4 TFLOPSに達する。ゲームで活用するのが大変そう。

| GPU | Lovelace AD102 | Ampere GA102 | Turing TU102 |

|---|---|---|---|

| 製造プロセス | 5nm Samsung(?) | 8nm Samsung | 12nm TSMC |

| GPC | 12(?) | 7 | 6 |

| TPC | 72(?) | 42 | 36 |

| SMs | 144(?) | 84 | 72 |

| CUDAコア | 18,432(?) | 10,752 | 4,608 |

| FP32演算性能(@ 1.8 GHz) | 66.4 TFLOPS(?) | 38.7 TFLOPS | 16.6 TFLOPS |

| メモリーバス幅 | 384-bit(?) | 384-bit | 384-bit |

| VRAM | GDDR6X(?) | GDDR6X | GDDR6 |

| 投入時期 | 2021 – 2022(?) | 2020 | 2018 |

CUDAコアがGA102 GPUから+71.4%も増えているにも関わらず、Hopperから採用されると言われている複数コアを1チップに実装するMCM (Multi-Chip Module)ではなく、Lovelaceではこれまでと同じくモノリシックなアーキテクチャとなる見込みで、膨大な数のトランジスタを1ダイに詰め込んだGPUになりそう。

なお、製造はSamsungの5 nmプロセス(5LPE?)になるとのこと。GA102で採用されているSamsungの8 nmノード(8LPP)のトランジスタ密度は最大61.18 MTr/mm2と推定されており、5LPEでは126.89 MTr/mm2まで密度が向上しているため、理論上はGA102と同サイズでAD102が作れることになるが、歩留まりが心配になる……

コメント